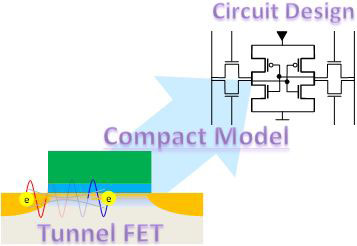

En una investigación colaborativa de nanoelectrónica verde dirigida por Koichi Fukada se desarrolló un modelo compacto para una simulación de circuito que ayuda a predecir el comportamiento de FETs de efecto tunel (Field-Effect Transistors).

Éste aparato simula características corriente-voltaje por medio de la predicción de la distribución del campo eléctrico en un FET de tunel y estimando la corriente. Este aparato puede ser incorporado en simuladores de circuitos mayores. Se espera que éste modelo contribuya al diseño de FETs apuntando a la realización de circuitos con poco poder.

Los detalles de ésta tecnología fueron presentados del 25 al 27 de Septiembre del 2012 en la Conferencia internacional de Dispositivos y Materiales de Estádo Sólido o SSDM por sus siglas en inglés que se llevó a cabo en Kyoto.

Para más información visitar: Nanowerk

No hay comentarios:

Publicar un comentario